# **AnadigmFilter1 Evaluation Board Quick Start User Guide**

PLEASE read all of this minimal document before starting. It may save you a lot of time.

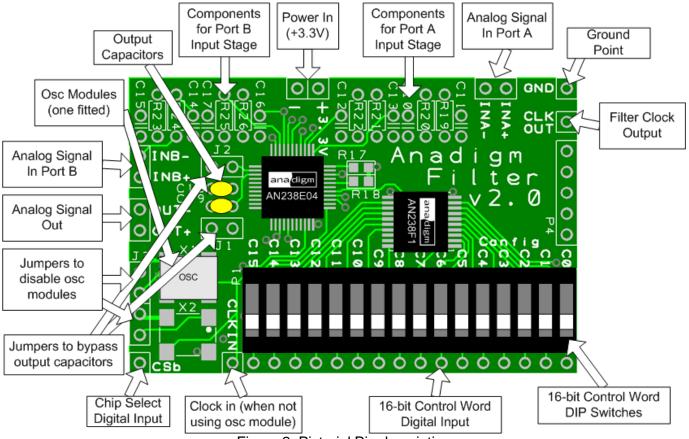

Figure 1 below shows a photo of the AnadigmFilter1 Evaluation Board.

Figure 1.

### **Quick start instructions:**

- 1. Power up the board by connecting it to a +3.3V power supply.

- 2. Connect a ground referenced differential signal to INA+ and INA-. If the signal is single-ended, connect it to INA+ and connect INA- to ground.

- 3. Set configuration bits C13 and C11 high. This will enable input port A and set the gain to 0dB (x1).

- 4. Monitor the differential output on OUT+ and OUT-. The output signal will be filtered by a lowpass Butterworth filter with corner frequency 400kHz. See below for details of how to calculate corner frequency for different configuration settings and different master clock frequencies.

To calculate the corner or center frequency of any filter use the following equation

CORNER FREQUENCY = (F(aclk) / "Divisor\_B") \* "Divisor\_A" \* "Divisor\_C"

F(aclk) is the external clock frequency applied to the AN231E04 device ACLK pin.

Divisor A, B and C, see table below.

| A            |              |                         |              |      | ( D'' ()     | e•                               | ***                          | 1        |           |     |

|--------------|--------------|-------------------------|--------------|------|--------------|----------------------------------|------------------------------|----------|-----------|-----|

| Anadig       | gmFilterl    | l (lower 8              | bits of the  | ne 1 | 6 Bit Co     | nfigurati                        | on Word)                     |          |           |     |

|              | ternal Clock | sor_B<br>divider settii | 0            |      |              | <b>Divisor_</b> A Filter Fc sett | Divisor_(<br>Filter topology |          |           |     |

| ,            |              | Fc in octave steps)     |              |      | ,            | steps across                     |                              |          | Fc fac    | tor |

| <b>B4</b>    | B3           | B2                      | B1           |      | A3           | A2                               | A1                           |          |           | +   |

| C6<br>Pin 13 | C5<br>Pin 14 | C4<br>Pin 15            | C3<br>Pin 16 |      | C2<br>Pin 17 | C1<br>Pin 18                     | C0<br>Pin 19                 |          |           | +   |

|              |              |                         |              |      |              |                                  | DivisorA                     |          |           | +   |

|              | B4,B3,B2,B1  |                         | DivisorB     |      | A3,A2,A1     |                                  |                              |          | 1         | ╄   |

| 0000         |              | 1                       |              |      | 000          |                                  | 1.0                          |          | low pass  | 4   |

| 0001         |              | 2                       |              |      | 001          |                                  | 0.917                        |          | High Pass |     |

| 0010         |              | 4                       |              |      | 010          |                                  | 0.841                        |          | Bandpass  |     |

| 0011         |              | 8                       |              |      | 011          |                                  | 0.771                        |          | Bandstop  |     |

| 0100         |              | 16                      |              |      | 100          |                                  | 0.707                        |          |           |     |

| 0101         |              | 32                      |              |      | 101          |                                  | 0.648                        |          |           |     |

| 0110         |              | 64                      |              |      | 110          |                                  | 0.595                        |          |           |     |

| 01           | 0111         |                         | 128          |      | 111          |                                  | 0.545                        |          |           |     |

| 10           | 1000         |                         | 256          |      |              |                                  |                              | <u>.</u> |           |     |

| 10           | 1001         |                         | 512          |      |              |                                  |                              |          |           |     |

| 10           | 1010         |                         | 1024         |      |              |                                  |                              |          |           |     |

| 10           | 1011         |                         | 2048         |      |              |                                  |                              |          |           |     |

| 11           | 100          | 40                      | 096          |      |              |                                  |                              |          |           |     |

|              | 101          | 8:                      | 192          |      |              |                                  |                              |          |           |     |

|              | 110          |                         | 384          |      |              |                                  |                              |          |           |     |

|              | 111          |                         | 768          |      |              |                                  |                              |          |           |     |

|              |              |                         |              |      |              |                                  |                              |          |           |     |

- 5. The board comes with an 8MHz oscillator module. This can be replaced by another or disabled and an external clock applied to the CLK IN pin. The oscillator module can be disabled by applying a jumper or short to J3. Note: stopping the external clock makes the filter go into deep sleep mode (~20uW) regardless of control word setting.

- 6. The filter clock is output on pin CLK OUT. The filter clock is the master clock divided by Divisor\_B.

- 7. Set C11 low and C12 high. The input signal can now be applied to input port B. If both C11 and C12 are high then signals on both port A and port B will be summed.

- 8. Configuration bits C13 15 allow adjustment of the gain from 0dB to 18dB in 3dB steps.

- 9. If jumpers are applied to J1 and J2 then the output capacitors will be shorted. This means that the differential output signal will have a common mode voltage level of +1.5V.

- 10. See the table called "AnadigmFilter1 Control Interface" later in this document for details on how to set the different filter types and the limiting frequency for each type.

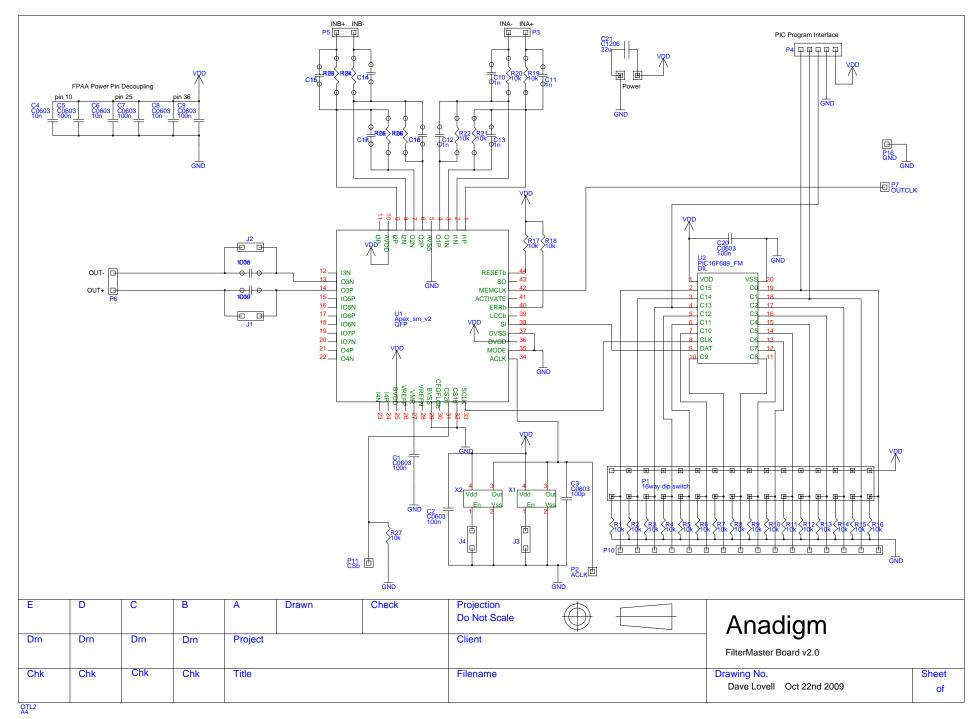

- 11. The input stages (see fig 3 and also schematic) consist of through hole capacitors (C10-17) and resistors (R19-26) combined with the input opamp of the dpASP. This input stage can be configured by the user to provide fixed filtering, gain and voltage step-up. The dpASP uses +1.5V centered signals but the input stages allow the user to drive the board with ground referenced signals. The through-hole resistors provided are 10k ohm and give a gain of x1. Note that the dpASP cannot be driven by a signal whose differential amplitude is greater than +/-3V (because signals on its pins IxP & IxN must be between 0 and +3V) so if the signal to the board is greater than +/-3V then the input stage should be configured to give a gain of < x1 (e.g. i/p +/-6V, make gain x0.5). The capacitors are not populated but can be added by the user to provide the desired (fixed) filtering on the input stage e.g. adding feedback caps to C12,13 or C16,17 will make a lowpass input filter (formula for Rs & Cs is standard).

v max

0.05 0.01 0.05 0.03

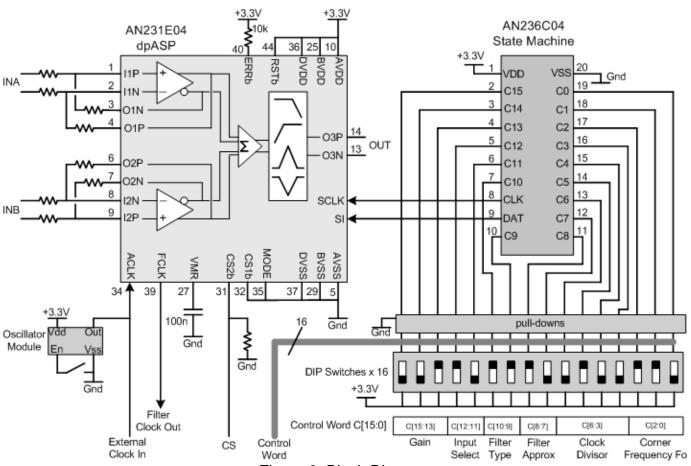

Figure 2, Pictorial Pin description

Figure 3, Block Diagram

| ANADIGM AnadigmFilter1 Control Interface (16 Bit Configuration Word) |                             |     |                              |        |                |                      |                                                 |                                         |                               |                                                                                        |        |           |           |                                                             |           |           |  |

|----------------------------------------------------------------------|-----------------------------|-----|------------------------------|--------|----------------|----------------------|-------------------------------------------------|-----------------------------------------|-------------------------------|----------------------------------------------------------------------------------------|--------|-----------|-----------|-------------------------------------------------------------|-----------|-----------|--|

| Gain Settings                                                        |                             |     | Analog Input Pin<br>settings |        |                | Filter Topology      |                                                 | Filter<br>approximation                 |                               | <b>DivisorB</b> Internal Clock divider settings, (divider to scale Fc in octave steps) |        |           |           | <b>DivisorA</b> Filter Fc settings (9% steps across octave) |           |           |  |

| MSB                                                                  |                             |     |                              |        |                |                      |                                                 |                                         |                               | ,                                                                                      |        |           | ,         | ,                                                           | •         | LSB       |  |

| <b>G3</b>                                                            | G2 G                        | 1   | <b>I2</b>                    | ,      | <b>I1</b>      | <b>T4</b>            | <b>T3</b>                                       | <b>T2</b>                               | <b>T1</b>                     | <b>B4</b>                                                                              | В3     | <b>B2</b> | <b>B1</b> | <b>A3</b>                                                   | <b>A2</b> | <b>A1</b> |  |

| C15                                                                  | C14 C1                      | 13  | <b>C</b> 1                   | 2      | C11            | C10                  | C9                                              | C8                                      | <b>C</b> 7                    | C6                                                                                     | C5     | C4        | C3        | C2                                                          | C1        | C0        |  |

| Pin 2                                                                | Pin 3 Pin                   | n 4 | Pin                          | 5      | Pin 6          | Pin 7                | Pin 10                                          | Pin 11                                  | Pin 12                        | Pin 13                                                                                 | Pin 14 | Pin 15    | Pin 16    | Pin 17                                                      | Pin 18    | Pin 19    |  |

| G3,G2,G1                                                             | Gain (dBs)                  |     | 12,1                         |        | Active nput(s) | T4,T3                | Filter<br>topology                              |                                         |                               | B4,B3,B2,B1                                                                            |        | DivisorB  |           | A3,A2,A                                                     | DivisorA  |           |  |

| 000                                                                  | -infinity (Mute)            |     | 00                           | )      | None           | 00                   | Lowpass                                         |                                         | Filter                        | 0000                                                                                   |        | 1         |           | 000                                                         |           | 1.0       |  |

| 001                                                                  | 0.0                         |     | 01                           | I      | Input A        | 01                   | Highpass                                        |                                         | Approximation applied depends |                                                                                        | 0001   |           | 2         |                                                             | 001 0.91  |           |  |

| 010                                                                  | 3.0                         |     | 10                           | ) I    | Input B        | 10                   | Bandpass                                        | upon the Filter                         |                               | 0010                                                                                   |        | 4         |           | 010                                                         |           | 0.841     |  |

| 011                                                                  | 6.0                         |     |                              |        | A & B          | 11                   | Bandstop                                        | topology                                | topology selected.            |                                                                                        | 0011   |           | 8         |                                                             | 011 0     |           |  |

| 100                                                                  | 9.0                         |     | 11                           |        | Note1          |                      |                                                 | See Table insert to                     |                               | 0100                                                                                   |        | 16        |           | 100                                                         | 0.707     |           |  |

| 101                                                                  | 12.0                        |     |                              |        |                |                      |                                                 |                                         | the lower left                |                                                                                        | 0101   |           | 32        |                                                             |           | 0.648     |  |

| 110                                                                  | 15.0                        |     |                              |        |                |                      |                                                 |                                         |                               | 0110                                                                                   |        |           | 54        | 101<br>110                                                  |           | 0.595     |  |

| 111                                                                  |                             |     |                              |        |                |                      |                                                 |                                         |                               | 0111                                                                                   |        | 128       |           | 111                                                         | -         | 0.545     |  |

|                                                                      |                             |     | T2,T1                        | Commen | ı Width        | Lim                  | its (FCLK = AC                                  | LK / DivisorB                           | )                             | 1000                                                                                   |        |           | 256       |                                                             |           | 0.5 15    |  |

| Lowpass                                                              | 1                           |     | 00                           |        | n/a            | _                    |                                                 |                                         | LK(max) = 8MHz                |                                                                                        | 1001   |           | 512       |                                                             |           |           |  |

| Lowpass                                                              | Chebyshev                   | 00  | 01                           |        | n/a            | Max Fc               | = 500kHz @ FC                                   | CLK(max) = 101                          |                               |                                                                                        | 1024   |           |           |                                                             |           |           |  |

| Lowpass                                                              | Bessel                      | 00  | 10                           |        | n/a            | Max Fc               | = 250kHz @ F                                    | LK(max) = 5MHz $LK(max) = 10MHz$ $1011$ |                               |                                                                                        |        |           |           |                                                             |           |           |  |

| Lowpass                                                              | Bypass                      | 00  |                              |        | n/a            | _                    |                                                 | CLK(max) = 10MHz                        |                               |                                                                                        |        |           |           |                                                             |           |           |  |

| Highpass                                                             | Butterworth                 | 01  | 00                           |        | n/a            | _                    |                                                 | CLK(max) = 6MHz                         |                               | 11                                                                                     | .00    | 4096      |           |                                                             |           |           |  |

| Highpass                                                             | Chebyshev                   | 01  | 01                           |        | n/a            | Max Fc = 100kHz @ FC |                                                 | ` '                                     |                               | 11                                                                                     | .01    | 81        | 192       |                                                             |           |           |  |

| Highpass                                                             | Bessel                      | 01  | 10                           |        | n/a            | _                    | Max Fc = 50kHz @ FCLK(max) =                    |                                         |                               | 1110                                                                                   |        | 16384     |           |                                                             |           |           |  |

| Highpass                                                             | Bypass                      | 01  | 11                           |        | n/a            | _                    | Max Fc = 1000kHz @ FCl<br>Max Fc = 500kHz @ FCl |                                         | . ,                           |                                                                                        | .11    |           | 768       |                                                             |           |           |  |

| Bandpass                                                             | Inverse Chebyshev<br>Bessel | 10  | -                            | narrow | 10%            |                      |                                                 |                                         |                               | 11                                                                                     | . 1 1  | 32        | 700       |                                                             |           |           |  |

| Bandpass                                                             | Dessei                      | 10  | 01                           | narrow | 10%            | IVIAX FC             | Max Fc = 600kHz @ FCLK(max) = 12MHz             |                                         |                               |                                                                                        |        |           |           |                                                             |           |           |  |

#### Notes

Bandpass

Bandpass

Bandstop

Bandstop

Bandstop

Bandstop

10 10

10 11

11 00

11 01

11

11

10

11

wider

wider

narrow

narrow

wider

wider

40%

40%

20%

20%

80%

80%

Max Fc = 500kHz @ FCLK(max) = 10MHz

Max Fc = 600kHz @ FCLK(max) = 12MHz

Max Fc = 120kHz @ FCLK(max) = 4MHz

Inverse Chebyshev

Bessel

Inverse Chebyshev

Bessel

Inverse Chebyshev

Bessel

<sup>1)</sup> If inputs A and B are selected then the two active input signals will be summed.

<sup>2)</sup> Setting of five 0's for the control bits C[15:11] (zero gain and no inputs selected) makes AnadigmFilter go into standby (approx 20mW). Stopping the external clock makes dpASP go into deep sleep (< 20uW).

<sup>3)</sup> Max Fc, or maximum Filter Corner or Center Frequency limits have been determined for better than 1% accurate filter parameters, exceeding these limits will result in loss of filter accuracy.

<sup>4)</sup> Bypass filter approximation provides a flat response from d.c. to FCLK \* 0.1. (FCLK = ACLK / Divisor\_A inputs have no effect in this mode, gain and input select still apply.

<sup>5)</sup> Divisor\_A step size is mathematically equal to  $(8thsqrt(2) \text{ or } ((2)^{\land}(1/8).$

<sup>6)</sup> FCLK (= ACLK / DivisorB) is provided on an output pin from the AN231E04, the primary purpose of this signal is to enable synchronization of any subsequent ADC